頭歌計算機組成原理實驗報告 存儲系統(tǒng)設(shè)計——字庫芯片與MIPS寄存器文件集成

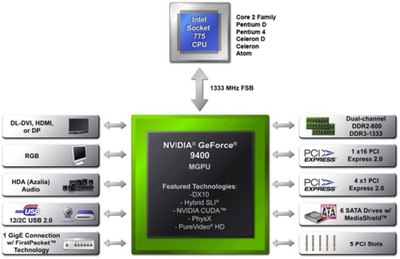

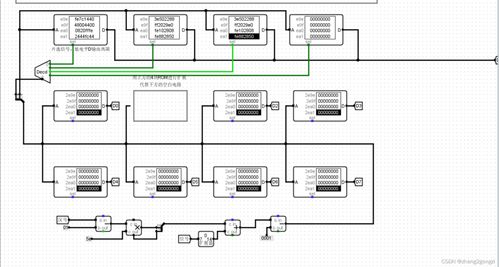

一、 實驗?zāi)康?/strong>\n1. 深入理解計算機存儲系統(tǒng)的基本組成與層次結(jié)構(gòu)。\n2. 掌握利用硬件描述語言(如Verilog或VHDL)設(shè)計特定功能存儲模塊(字庫存儲芯片)的原理與方法。\n3. 掌握MIPS架構(gòu)下寄存器文件(Register File)的設(shè)計、功能與實現(xiàn)細節(jié)。\n4. 實踐將獨立的存儲模塊(字庫芯片、寄存器文件)集成到一個完整的計算機原型系統(tǒng)或仿真測試平臺中,理解系統(tǒng)集成的流程與調(diào)試方法。\n\n二、 實驗原理\n1. 字庫存儲芯片設(shè)計:字庫芯片是一種用于存儲字符點陣信息的只讀存儲器(ROM)。實驗中,我們設(shè)計一個簡化字庫,例如存儲ASCII碼中部分可顯示字符的8x16點陣數(shù)據(jù)。核心原理是將字符的ASCII碼作為地址輸入,通過查找表(LUT)輸出對應(yīng)字符的一行點陣數(shù)據(jù)。設(shè)計需包括地址譯碼器、存儲矩陣和輸出驅(qū)動電路。\n2. MIPS寄存器文件設(shè)計:寄存器文件是CPU內(nèi)部的高速存儲單元,用于暫存指令操作數(shù)和結(jié)果。基于MIPS32架構(gòu),我們設(shè)計一個包含32個32位通用寄存器的模塊。關(guān)鍵功能包括:支持兩路讀操作(通過Read Reg1和Read Reg2端口同時讀取兩個寄存器的值)和一路寫操作(在Write Reg有效且時鐘邊沿到來時,將Write Data寫入目標寄存器)。需特別注意對\$zero寄存器(恒為0)的特殊處理。\n3. 系統(tǒng)集成:將上述兩個獨立的存儲模塊與實驗平臺提供的其他組件(如ALU、控制器、主存接口等)進行連接。集成的關(guān)鍵在于理解各模塊間的數(shù)據(jù)通路、控制信號(如讀/寫使能、片選信號)與時序配合,構(gòu)建一個能協(xié)同工作的最小系統(tǒng)。\n\n三、 實驗內(nèi)容與步驟\n1. 環(huán)境搭建:在頭歌(EduCoder)或本地安裝的FPGA開發(fā)工具(如Vivado、Quartus)中創(chuàng)建工程,選擇目標器件。\n2. 字庫芯片設(shè)計與仿真:\n - 使用HDL編寫字庫ROM模塊。初始化內(nèi)容可預(yù)先存儲在.coe或.hex文件中,或在代碼中用數(shù)組定義。\n - 編寫測試平臺(Testbench),驗證輸入特定ASCII碼時,能否正確輸出對應(yīng)的點陣行數(shù)據(jù)。\n3. MIPS寄存器文件設(shè)計與仿真:\n - 使用HDL編寫寄存器文件模塊,實現(xiàn)雙讀單寫功能。\n - 編寫測試平臺,驗證讀寫功能是否正確,特別測試對\$zero寄存器的讀操作是否恒為0,以及寫操作是否被忽略。\n4. 系統(tǒng)集成與功能驗證:\n - 在頂層模塊(Top Module)中實例化字庫芯片、寄存器文件以及其他必要模塊(如預(yù)定義的CPU核或總線接口)。\n - 設(shè)計集成測試方案:例如,編寫一段簡單的控制流程,將字符代碼從某個寄存器讀出,送入字庫芯片獲取點陣數(shù)據(jù),再存入另一寄存器或輸出到顯示緩沖區(qū)(仿真中可用變量模擬)。\n - 進行系統(tǒng)級仿真,觀察信號波形,確保數(shù)據(jù)在各模塊間正確流動。\n5. 綜合與實現(xiàn)(可選,取決于平臺要求):將設(shè)計綜合到目標FPGA,分配管腳,生成比特流文件。\n\n四、 實驗結(jié)果與分析\n1. 仿真波形截圖與分析:\n - 展示字庫芯片仿真波形:輸入地址(字符代碼)變化時,輸出數(shù)據(jù)隨之正確變化。\n - 展示寄存器文件仿真波形:同時讀取兩個寄存器的值,并在時鐘控制下成功寫入第三個寄存器,且\$zero寄存器行為符合預(yù)期。\n - 展示系統(tǒng)集成仿真波形:演示從寄存器取址->字庫查表->結(jié)果回寫的完整數(shù)據(jù)通路工作正常。\n2. 關(guān)鍵代碼段說明:\n - 字庫模塊的查找表定義與地址映射邏輯。\n - 寄存器文件的讀寫端口實現(xiàn)與\$zero寄存器處理邏輯。\n - 頂層模塊中連接各子模塊的端口映射與信號連接代碼。\n3. 故障與調(diào)試記錄:記錄實驗過程中遇到的主要問題(如時序沖突、信號未初始化、地址位寬不匹配等)及解決方法。\n\n五、 實驗與思考\n1. **:本次實驗成功設(shè)計并實現(xiàn)了字庫存儲芯片和MIPS寄存器文件兩個核心存儲模塊,并通過系統(tǒng)集成驗證了其協(xié)同工作能力。加深了對ROM、寄存器文件工作原理以及計算機系統(tǒng)數(shù)據(jù)通路構(gòu)建的理解。\n2. 思考題:\n - 字庫芯片如果采用異步讀取和同步讀取,在設(shè)計上有何不同?對系統(tǒng)時序有何影響?\n - MIPS寄存器文件采用同步寫操作,為什么讀操作通常是異步的(組合邏輯輸出)?這種設(shè)計有什么優(yōu)缺點?\n - 在更大規(guī)模的系統(tǒng)集成中,如何解決多個存儲模塊訪問總線時的沖突問題?\n3. 心得體會**:通過本次動手實驗,不僅鞏固了理論知識,更掌握了使用現(xiàn)代EDA工具進行數(shù)字系統(tǒng)設(shè)計、仿真與調(diào)試的完整流程,對計算機硬件系統(tǒng)的“自底向上”構(gòu)建過程有了更直觀的認識。

如若轉(zhuǎn)載,請注明出處:http://www.dongfengnissan.cn/product/58.html

更新時間:2026-01-06 01:18:19